Solilock-G

Solilock-GはGHz帯を直接発振するVCOを使ったPLL発振器です。

Solilock-Gには様々なバリエーションがあります。

動作方式は

(type1)外部から基準信号(普通は10MHz)を入力し、発振周波数を10MHzステップで設定する物。位相比較周波数は10MHzです。

(type2)外部から基準信号(普通は10MHz)を入力し、発振周波数を5kHzステップで設定する物。位相比較周波数は10MHzまたは20MHzです。

周波数帯は

(band1)4.4〜5.0GHz

(band2)5.0〜5.5GHz

(band3)5.5〜6.1GHz

(band4)5.8〜6.8GHz

の4種類の実績があります。

(type1,2) x (band1〜4) の組み合わせが可能です。

出力レベルは5dBm以上です。

・製作例1 6275MHz

・製作例2 5896.25MHz

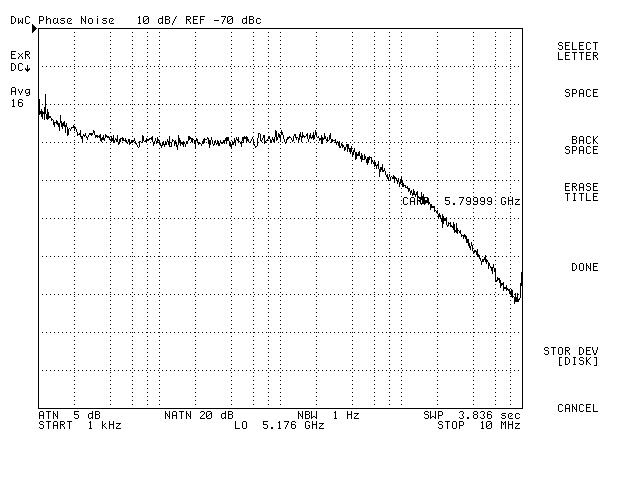

・製作例3 5800MHz

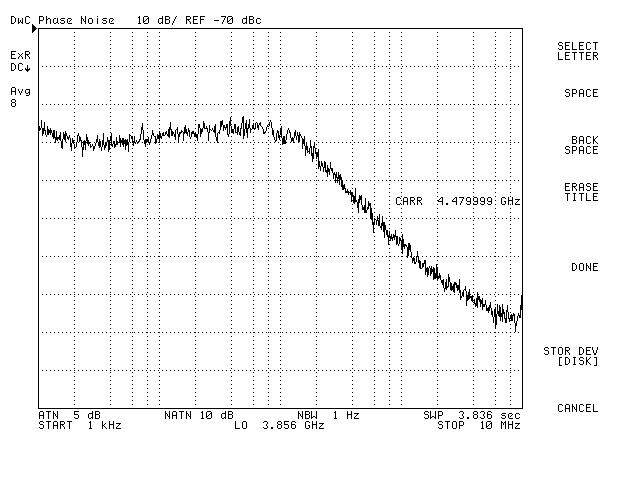

・製作例4 4480MHz(4440MHz〜4560MHz)

・製作例5 24020MHz(24.02GHz)

・応用例1 EME用10GHz帯トランスバータへの組込

・位相ノイズ測定・基準信号について・電源ノイズの影響

製作例1 6275MHz

これはSolilock-G (type1 band4)の例です

スペアナで見るとこんな感じです。

SPAN=100kHz、RBW=1kHzです。Solilock-G出力端からスペアナ入力までに約6dBの損失があります。

位相雑音は10kHzオフセットで-90dBc/Hz、1MHzオフセットで-117dBc/Hzくらいです。

原理的に、

(1)発振周波数が高い方がC/Nは悪くなります。この製作例は6275MHzと比較的高い周波数なので、C/NはSolilock-Gのワーストケースと考えます。

(2)位相比較周波数が低い方がC/Nが悪くなります。この製作例は位相比較周波数が5MHzなので、キリの良い10MHzよりもC/Nが悪いです。

周波数が低く、キリの良い周波数(たとえば4480MHz等)では位相雑音は-95dBc/Hz以下になります。

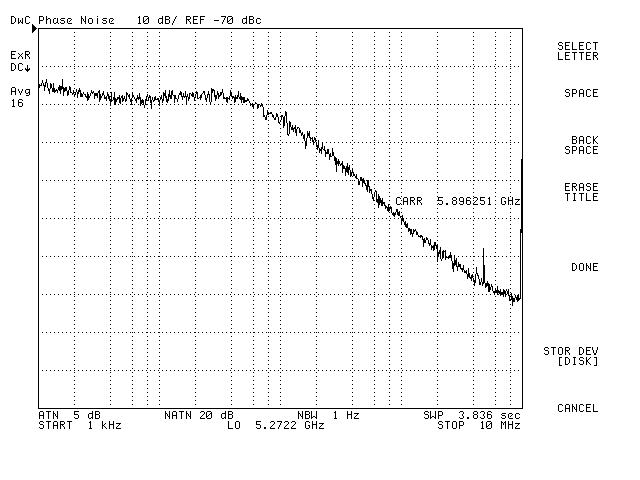

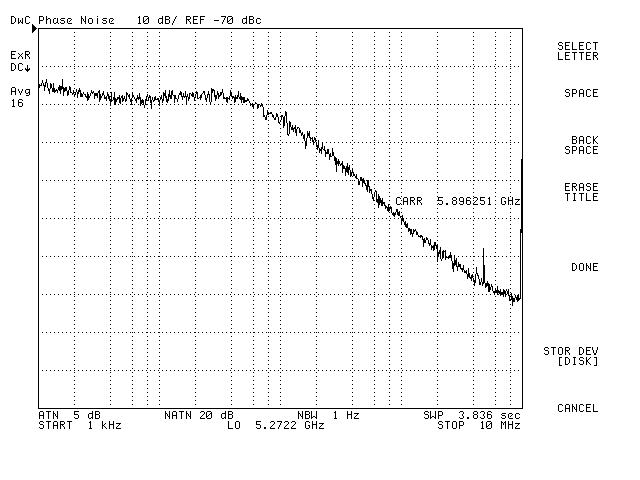

製作例2 5896.25MHz

type2 band4の組み合わせです。

type1(Integer-N PLL)で5896.25MHzを10MHzの基準信号から作ろうとすると、位相比較周波数が1.25MHzになってしまいます。

以下のようにC/Nが高くできない可能性があります。

(1)位相比較周波数が低いのでC/Nが悪くなる。

(2)リファレンスリークを防ぐためにループ帯域を最適帯域よりも狭くする。このため、C/Nが悪くなる。

そこで、Fractional-N PLLで位相比較周波数よりも低い周波数分解能のPLLを構成します。

位相雑音は10kHzオフセットで-88dBc/Hz、1MHzオフセットで-120dBc/Hzくらいです。

位相雑音は-88dBc/Hzくらいです。

integer-Nに比べると若干ノイズは多いですが、Fractional-Nにすることでキリの良くない周波数も実現が可能になります。

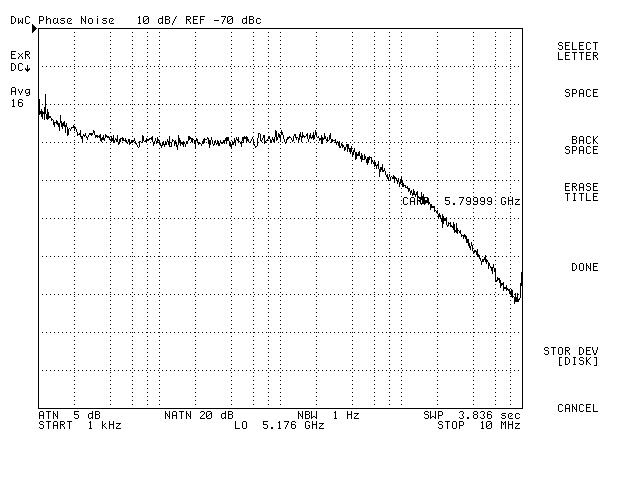

製作例3 5800MHz

位相比較周波数を高くするとC/Nを高くすることが出来ます。

Solilock-Gへ供給する基準信号を100MHzとし、位相比較周波数を20MHzにしたものです。

位相雑音は10kHzオフセットで-100dBc/Hz、1MHzオフセットで-110dBc/Hzくらいです。

-100dBc/Hzが達成出来ました。5840MHzでも同様です。

この製作例では、ループの帯域幅を広く取っています。そのため、100kHz以上の雑音が他の製作例に比べて高めになっています。

局発用として使う場合は製作例1,2の様に帯域幅を最適化します。

基準信号に10MHzを使うことが多いですが、可能であれば基準信号は100MHz以上にした方がよいと思います。

製作例4 4480MHz(4440MHz〜4560MHz)

1200MHzの親機に接続する5G帯、10G帯のトランスバータによく使う周波数でです。

ジャンパーSWの設定で4480MHzのほか、4440MHz、4520MHz、4560MHzに切り替え可能です。

送信、受信で4480/4440を切り替えればレピーター対応になります。

ジャンパーSWと発振周波数

| 設定番号 |

JP3 |

JP2 |

JP1 |

周波数 |

基準信号 |

SWポジション |

5G帯の周波数 |

主な使用区分 |

| 0 |

OPEN |

OPEN |

OPEN |

4480 |

10MHz |

2 |

5740〜5780 |

5GHz帯、10GHz帯シンプレックス |

| 1 |

OPEN |

OPEN |

GND |

4440 |

10MHz |

1 |

5700〜5740 |

ATV、高速データ

レピータアップリンク |

| 2 |

OPEN |

GND |

OPEN |

4520 |

10MHz |

3 |

5780〜5820 |

全電波形式 |

| 3 |

OPEN |

GND |

GND |

4520 |

10MHz |

|

|

|

| 4 |

GND |

OPEN |

OPEN |

4560 |

10MHz |

4 |

5820〜5850 |

衛星バンド |

| 5 |

GND |

OPEN |

GND |

4560 |

10MHz |

|

|

|

| 6 |

GND |

GND |

OPEN |

4480 |

100MHz |

|

|

|

| 7 |

GND |

GND |

GND |

4560 |

100MHz |

|

|

|

・一般的には、すべてのジャンパーをOPENにして、4480MHzを発振させます。

・5700MHz〜5850MHzをカバーさせるために、1回路4接点のロータリースイッチを用意し、JP1、JP2、JP3のいずれかをGNDするように配線します。

・送信時にJP1をGNDに落とす回路を追加すると送信時4440MHz、受信時4480MHzとなり、親機をシフトさせなくてもレピータの運用が可能になります。(レピータがあれば・・・)

・4480MHzと4560MHzは基準信号として100MHzの信号を利用する設定も組み込んであります。バンド内の位相ノイズを-100dBc程度に抑えられます。4560MHzはUNITEC-1のダウンリンク(5840MHz)受信用です。

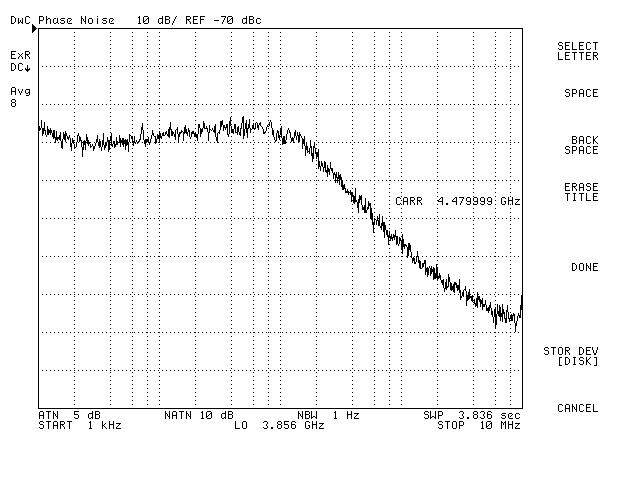

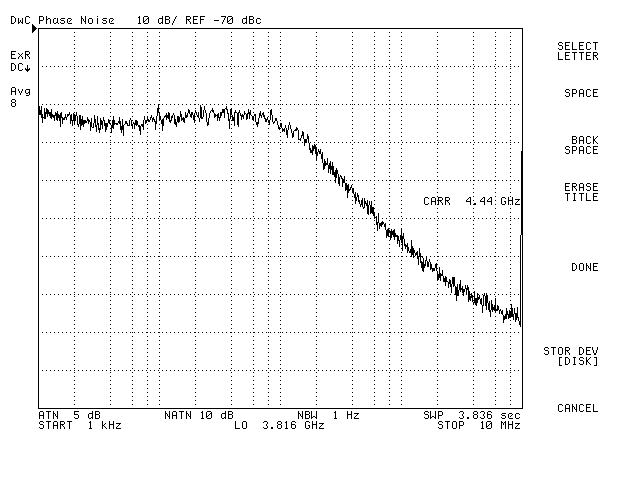

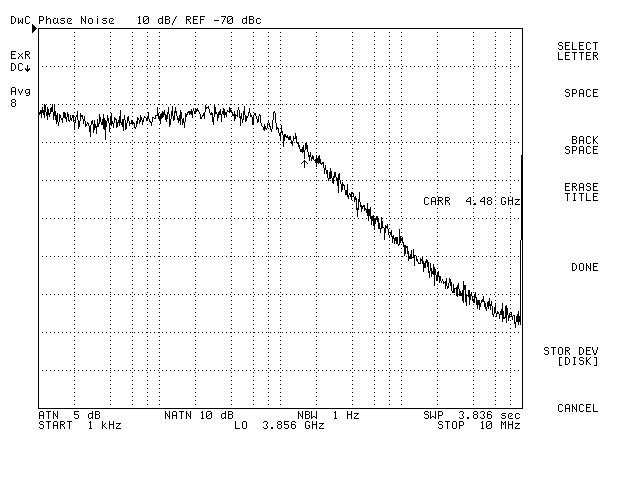

4480MHzの位相ノイズ(基準信号100MHz)

位相雑音は10kHzオフセットで-98dBc/Hz、1MHzオフセットで-126dBc/Hzくらいです。

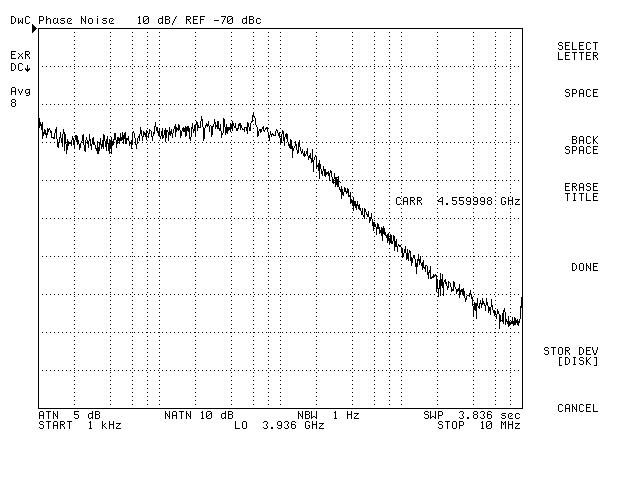

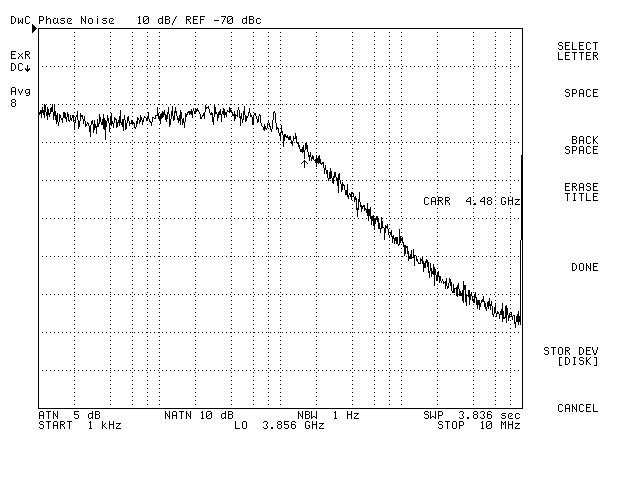

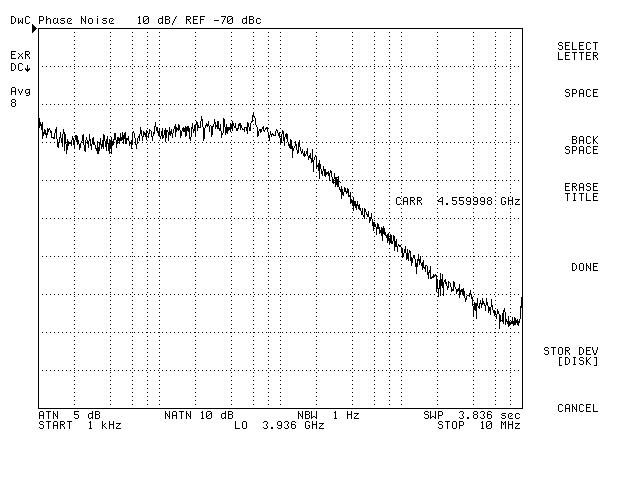

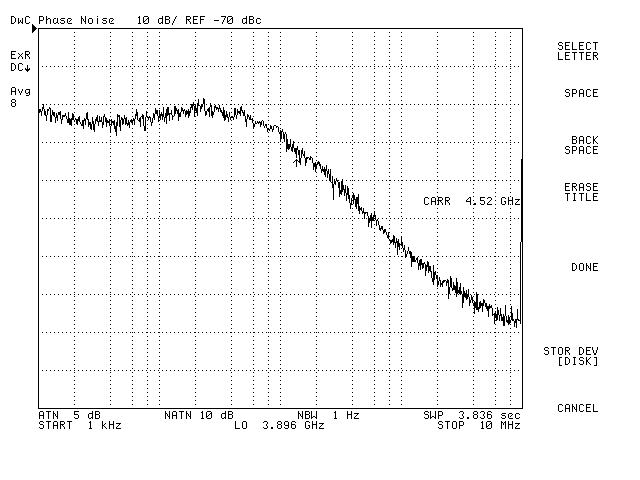

4560MHzの位相ノイズ(基準信号100MHz)

位相雑音は10kHzオフセットで-97dBc/Hz、1MHzオフセットで-128dBc/Hzくらいです。

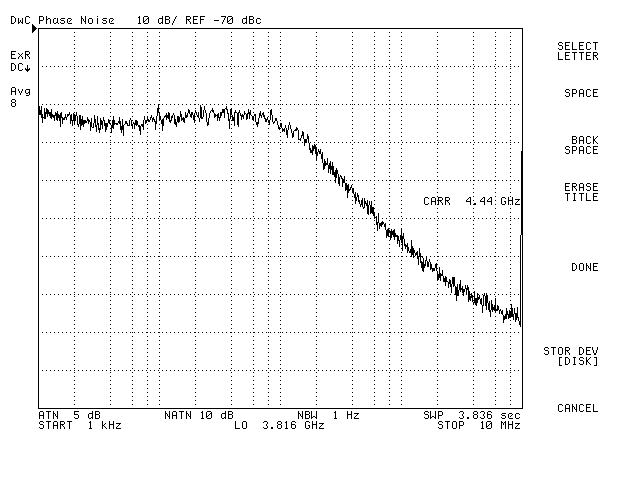

4440MHzの位相ノイズ(基準信号10MHz)

位相雑音は10kHzオフセットで-94dBc/Hz、1MHzオフセットで-126dBc/Hzくらいです。

4480MHzの位相ノイズ(基準信号10MHz)

位相雑音は10kHzオフセットで-93dBc/Hz、1MHzオフセットで-127dBc/Hzくらいです。

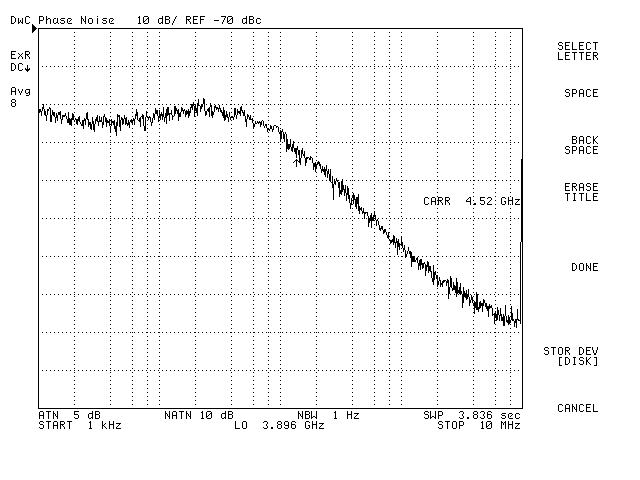

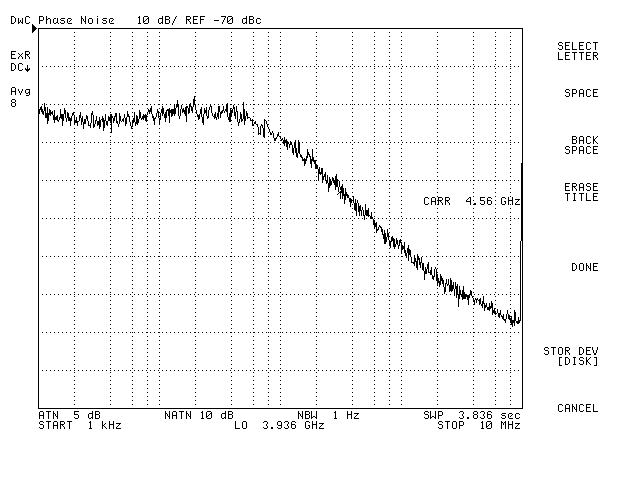

4520MHzの位相ノイズ(基準信号10MHz)

位相雑音は10kHzオフセットで-93dBc/Hz、1MHzオフセットで-127dBc/Hzくらいです。

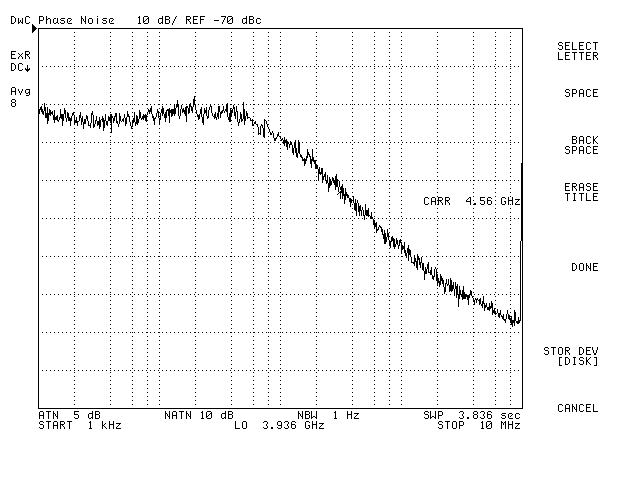

4560MHzの位相ノイズ(基準信号10MHz)

位相雑音は10kHzオフセットで-93dBc/Hz、1MHzオフセットで-127dBc/Hzくらいです。

応用例

たとえば以下のような応用例が考えられます。

・ トランスバータの局発としてよく使われる4480MHz の発振回路

・ 同様に、IF=430MHz としたときの5200MHz 帯の発振回路

・ 逓倍することで10GHz 帯以上の局発として使える5000MHz〜7000MHz の発振回路

・ 5700MHz 帯アマチュアバンドの信号源として使える発振回路

JA1WQFによるトランスバータへの組込例

10GHzのJA-EME、海外EMEを1台のトランスバータで対応させるために、局発の周波数を切替えます。Solilock-Gならば8chまでプリセット可能です。

ch設定端子をつかって、4553MHzと4594MHzを即座に切り替えています。

詳細はこちら

プリセット周波数

Solilock-Gは、あらかじめ8chの周波数を記憶させておけます。

さらに、WindowsパソコンからSolilock Configuratorというプログラムを使って周波数の設定値を書き換えることが出来ます。

以下続く

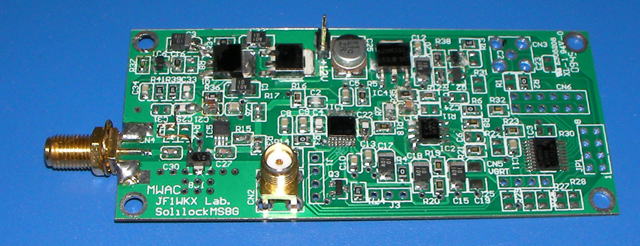

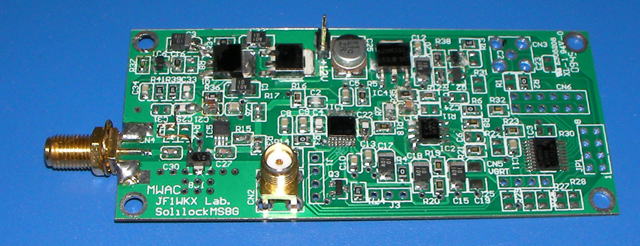

以下はSolilockGの初期開発時の記事

Solilock for GHzのつもり

構成は

PLL : ADF4107

CPU : MSP430F1121A

VCO : HMC429LP4

hittiteのVCOでパッケージがLP4のものならみんな使える筈。

VCOを取り付けずに、外部のVCOを制御することも可能。

今回の試作は、LP4が手半田出来るか否かの見極めの意味も大。

現在、火入れとデバッグの途中

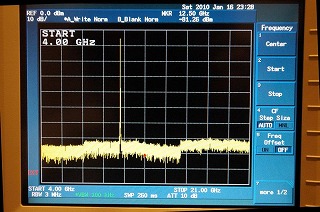

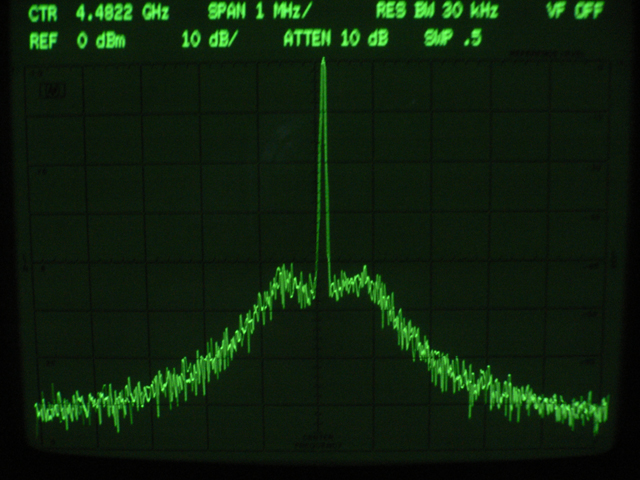

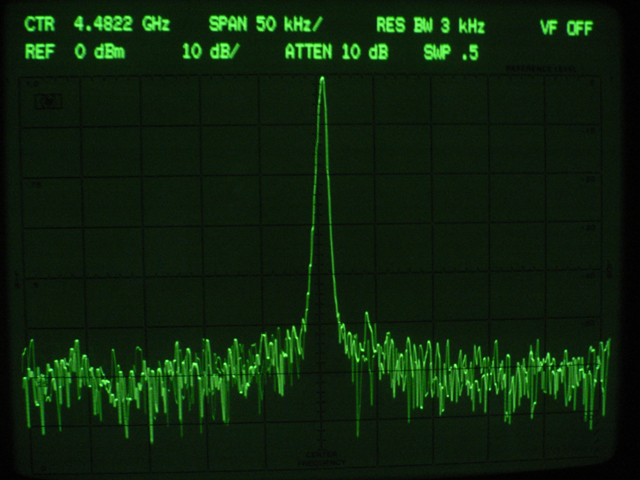

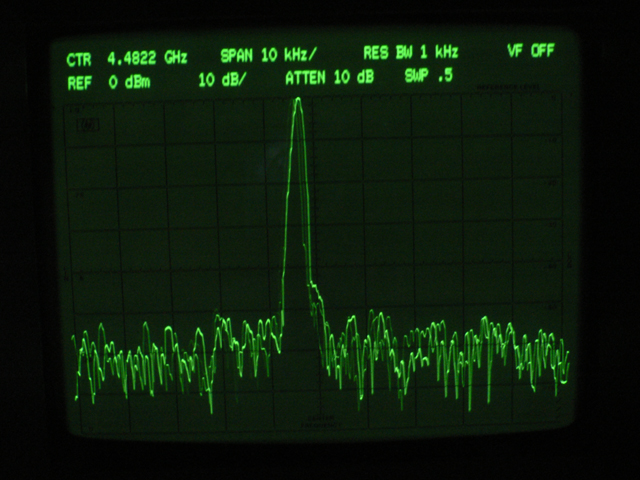

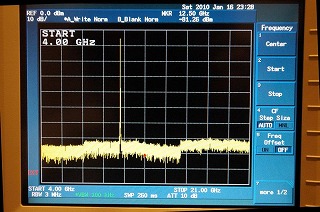

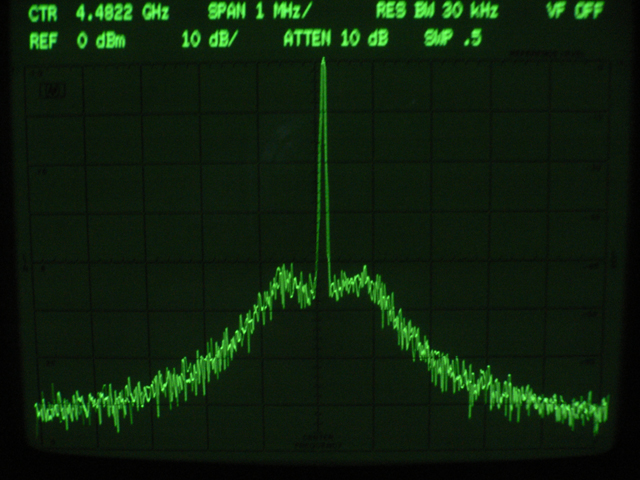

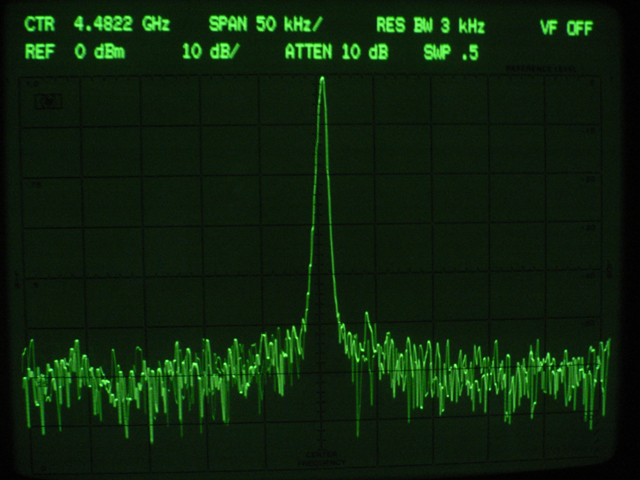

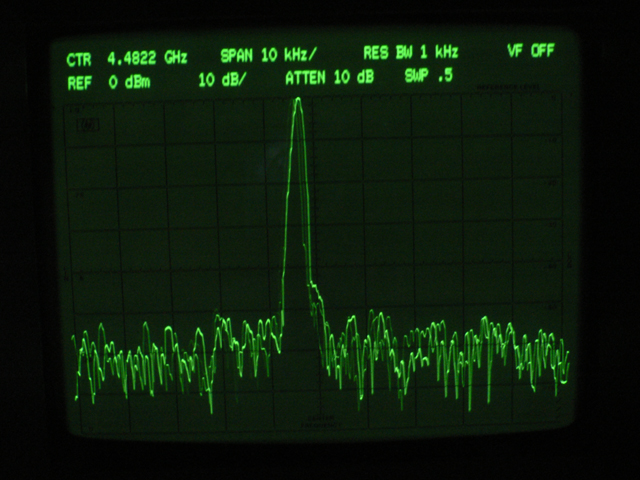

4480MHzを発振させてスプリアスを見ました。

オールドファッションなスペアナでごめんなさい。スペアナの周波数がこけてます。

1MHz離調で-55dBc。RBW=30KHzなので、都合良く解釈すると、-55-10log(30000)で-100dBc/Hz。

100kHz離調で-60dBc。RBW=3KHzなので、都合良く解釈すると、-60-10log(3000)で-95dBc/Hz。

10kHz離調で-60dBc。RBW=1KHzなので、都合良く解釈すると、-60-10log(1000)で-90dBc/Hz。

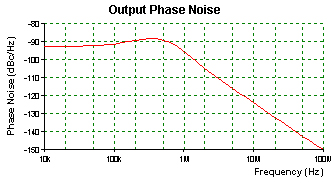

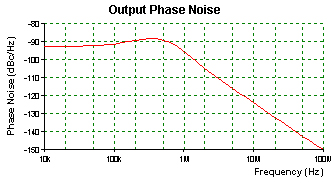

ADIsimPLLでのPhaseNoiseの予測。

ほぼ予測通り。

戻る